# **DEPARTMENT**

OF

# **ELETRONICS AND TELECOMMUNICATION ENGINEERING**

RAMAIAH INSTITUTE OF TECHNOLOGY

(Autonomous Institute, Affiliated to VTU)

**BENGALURU - 560054**

# III SEMESTER

# DIGITAL CIRCUIT DESIGN LAB MANUAL (ETL37)

2023-2024

**Faculty In-Charge:**

Dr. H R RAMYA Dr. PARIMALA PRABHAKAR Dr. K R SHOBHA

RAMAIAH INSTITUTE OF TECHNOLOGY (Autonomous Institute, Affiliated to VTU) BANGALORE – 54

## **About the Institute:**

Dr. M. S. Ramaiah a philanthropist, founded 'Gokula Education Foundation' in 1962 with an objective of serving the society. M S Ramaiah Institute of Technology (MSRIT) was established under the aegis of this foundation in the same year, creating a landmark in technical education in India. MSRIT offers 17 UG programs and 15 PG programs. All these programs are approved by AICTE. All eligible UG and PG programs are accredited by National Board of Accreditation (NBA). The institute is accredited with 'A+' grade by NAAC in March 2021 for 5 years. University Grants Commission (UGC) & Visvesvaraya Technological University (VTU) have conferred Autonomous Status to MSRIT for both UG and PG Programs since 2007. The institute has also been conferred autonomous status for Ph.D. program since 2021. The institute is a participant to the Technical Education Quality Improvement Program (TEQIP), an initiative of the Government of India. The institute has 380 competent faculty out of which 67% are doctorates. Some of the distinguished features of MSRIT are: State of the art laboratories, individual computing facility for all faculty members, all research departments active with sponsored funded projects and more than 300 scholars pursuing Ph.D. To promote research culture, the institute has established Centre of Excellence for Imaging Technologies, Centre for Advanced Materials Technology, Centre for Antennas and Radio Frequency systems (CARFS), Center for Cyber Physical Systems, Schneider Centre of Excellence & Centre for Bio and Energy Materials Innovation. Ramaiah Institute of Technology has obtained "Scimago Institutions Rankings" All India Rank 107 & world ranking 600 for the year 2022.

The Entrepreneurship Development Cell (EDC) and Section 8 company "Ramaiah Evolute" have been set up on campus to incubate startups. M S Ramaiah Institute of Technology is recognized by Atal Ranking of Institutions on Innovation Achievements (ARIIA), MoE, Govt. of India. MSRIT has a strong Placement and Training department with a committed team, a good Mentoring/Proctorial system, a fully equipped Sports department, large air-conditioned library with good collection of book volumes and subscription to International and National Journals. The Digital Library subscribes to online e-journals from Elsevier Science Direct, IEEE, Taylor & Francis, Springer Link, etc. The Institute is a member of DELNET, CMTI and VTU E-Library Consortium. The Institute has a modern auditorium, recording studio, and several hi-tech conference halls with video conferencing facilities. The institute has excellent hostel facilities for boys and girls. MSRIT Alumni have distinguished themselves by occupying high positions in India and abroad and are in touch with the institute through an active Alumni Association.

As per the National Institutional Ranking Framework (NIRF), MoE, Government of India, Ramaiah Institute of Technology has achieved 78<sup>th</sup> rank among 1314 top Engineering Institutions & 23<sup>rd</sup> Rank for School of Architecture in India for the year 2023.

# About the department:

The Department of Electronics & Telecommunication Engineering (Formerly known as Department of Telecommunication Engineering) was established in 1996 to address the increasing demand for professionals with expertise in communication and networking technology in India. The Department has state of the art laboratories, equipment's, resources and committed faculty having best of the academic and industry recognition. The Department started a **M.Tech program in Digital Communication in the year 2004**. The Department also started a **Research Centre** in the year 2012 and currently has 07 Research Scholars carrying

out their Research. Department has collaborations with some of the leading industries like **Ansys**, **Rohde & Schwarz**, **JV Micronics**, **Nokia**, **Huawei Technologies**, **Intel**, **Samsung**, and with leading national and international universities like **Bradley University**, **IIT-M**, enabling the department to focus on R&D, and thus providing new avenues for PG/UG students for placement and higher studies. Both UG and PG Programs are accredited by the **National Board of Accreditation**. There are **5 Funded Research projects** (Industry and Government) ongoing in the department involving students to carry out innovative projects. Many professional activities are organized regularly to the students under various professional societies like IEEE Sensor Council, IEEE Communication Society, IEEE Antenna and Propagation Society, IETE Bangalore and IEEE MTTs student Branch.

## VISION OF THE INSTITUTE

The department of ETE has established the Centre of Excellence – Centre for Antennas and Radio Frequency Systems (CARFS) Jointly with ECE department on 24th March 2021 to engage in advanced Research leading to innovation in the areas of Antennas & RF Systems. The CARFS has the State of the art Facilities to collaborate with Researchers in other Institutions across the Country and World in various projects.

To be an Institution of International Eminence, renowned for imparting quality technical education, cutting edge research and innovation to meet global socio- economic needs

## MISSION OF THE INSTITUTE

# RIT shall meet the global socio-economic needs through

- Imparting quality technical education by nurturing a conducive learning environment through continuous improvement and customization

- Establishing research clusters in emerging areas in collaboration with globally reputed organizations

- Establishing innovative skills development, techno-entrepreneurial activities and consultancy for socioeconomic needs

# **QUALITY POLICY**

We at Ramaiah Institute of Technology strive to deliver comprehensive, continually enhanced, global quality technical and management education through an established Quality Management System complemented by the synergistic interaction of the stake holders concerned

## VISION OF THE DEPARTMENT

To provide an ambience for the students to excel in studies, research and innovation, focusing on meeting global socio-economic needs from a Telecommunication Engineering perspective

## MISSION OF THE DEPARTMENT

- Providing high quality technical education to create world class Telecommunication engineers.

- Creating an ambience for skill development, research and entrepreneurial activities to meet socioeconomic needs

## PROGRAM EDUCATIONAL OBJECTIVES (PEOs):

- **PEO1:** Graduates will excel in professional careers in Industry, Academia and Research to meet Socio-Economic needs.

- **PEO2:** Graduates will analyze problems specific to Telecommunication Engineering and multidisciplinary domains providing technically feasible solutions.

- PE03: Graduates will exhibit professional communication skills, teamwork, leadership qualities, ethical behavior and lifelong learning.

## **PROGRAM OUTCOMES (POs):**

- **PO1: Engineering knowledge:** Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering specialization to the solution of complex engineering problems.

- PO2: Problem analysis: Identify, formulate, review research literature, and analyze complex

engineering problems reaching substantiated conclusions using first principles of mathematics,

natural sciences, and engineering sciences.

- PO3: Design/development of solutions: Design solutions for complex engineering problems

and design system components or processes that meet the specified needs with appropriate

consideration for the public health and safety, and the cultural, societal, and environmental

considerations.

- PO4: Conduct investigations of complex problems: Use research-based knowledge and research methods including design of experiments, analysis and interpretation of data, and synthesis of the information to provide valid conclusions.

- PO5: Modern tool usage: Create, select, and apply appropriate techniques, resources, and

modern engineering and IT tools including prediction and modeling to complex engineering

activities with an understanding of the limitations.

- **PO6:** The engineer and society: Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal and cultural issues and the consequent responsibilities relevant to the professional engineering practice.

- PO7: Environment and sustainability: Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.

- PO8: Ethics: Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice.

- **PO9: Individual and team work:** Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings.

- PO10: Communication: Communicate effectively on complex engineering activities with the

engineering community and with society at large, such as, being able to comprehend and write

effective reports and design documentation, make effective presentations, and give and receive

clear instructions.

- PO11: Project management and finance: Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments.

- **PO12:** Life-long learning: Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change.

# PROGRAM SPECIFIC OUTCOMES (PSOs):

•

- **PSO1:** Identify, analyze, formulate, design and demonstrate applications relevant to telecommunication engineering using electronic devices.

- **PSO2:** Use current technology and modern tools to address solutions for telecommunication products by taking into account safety, healthy environmental requirements.

- PSO3: Apply project management tools to solve Telecommunication systems by exhibiting teamwork, lifelong learning.

# COURSE DESIGN, DELIVERY AND ASSESMENT

| Course Code and Title: <b>Digital Circuit Design Lab</b> , Course Credits: 0:0:1 |                  |

|----------------------------------------------------------------------------------|------------------|

| ETL37                                                                            |                  |

| CIE: 50 Marks                                                                    | SEE: 50 Marks    |

| Total No of Lab Hours: 28 Hrs                                                    |                  |

| Prepared by :Dr.Ramya H R                                                        | Date: 15/11/2023 |

| Reviewd by : Dr.K R Shobha                                                       | Date: 15/11/2023 |

# **Prerequisites**

| D III C III I D I FI / (FC12)                             |  |

|-----------------------------------------------------------|--|

| Prerequisite Courses with codes: Basic Electronics (EC13) |  |

| Trerequisite courses with codes. Basic Electronics (EC13) |  |

## **COURSE OBJECTIVES:**

- 1. Demonstrating to students how to simplify, analyse and design combinational digital circuit.

- 2. Delivering to students how to build a sequential circuit (memory) using gates practically.

- 3. Appreciate the importance of Verilog HDL to design and verify digital circuit using EDA tools.

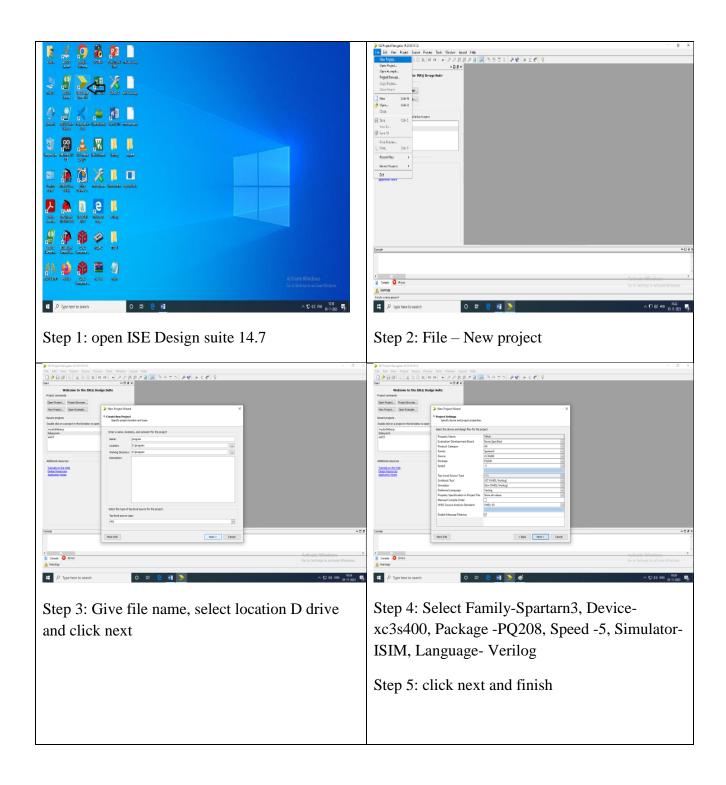

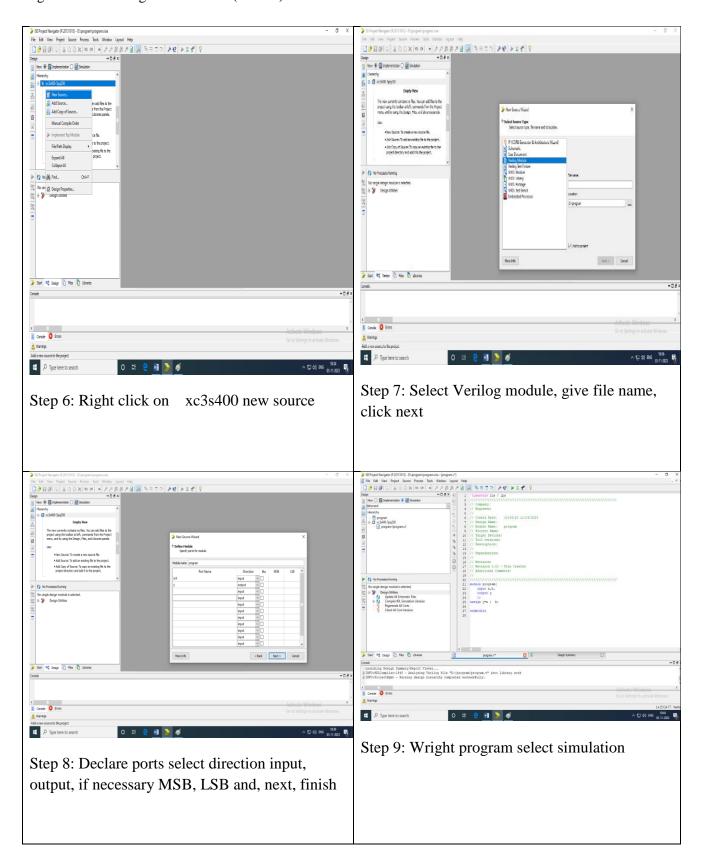

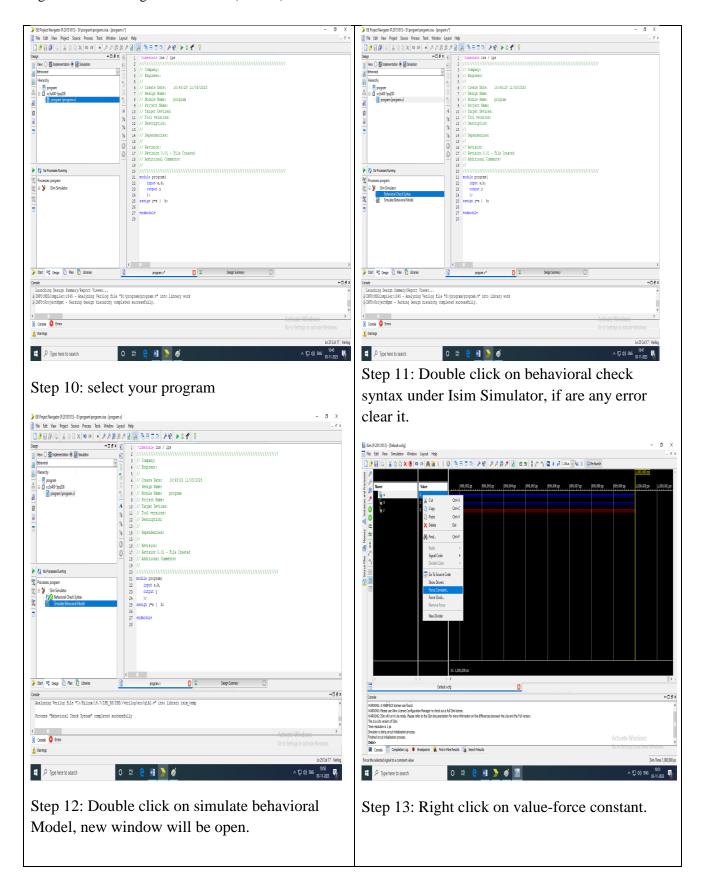

- 4. Understand the lexical conventions of VERILOG HDL at dataflow, gate level, structural, Behavioral and RTL levels.

- 5. Interpret Verilog constructs for logic synthesis using CAD tools. Discriminate between manual and automated logic synthesis and their impact on design. Discussing different FPGA architectures.

- **Note:** I) Student should design the logic circuit using **gates** and wiring the circuit using IC's & **trainer kit** to verify the design.

- II) Student should write the Verilog HDL module to simulate and synthesize the logic circuit using FPGA **XC3S400 IC** hardware board with **Xilinx 14.7i** software.

# **Content Sheet**

| SL NO | LIST OF EXPERIMENTS                                       | Page No |  |

|-------|-----------------------------------------------------------|---------|--|

| 1     | Simplification, realization of Boolean expressions        | 1-7     |  |

|       | using logic gates/Universal gates and Verilog HDL         |         |  |

|       | module                                                    |         |  |

| 2     | Realization of Half/Full adder and Half/Full              | 8-13    |  |

|       | subtractions using logic gates and Verilog HDL            |         |  |

|       | module                                                    |         |  |

| 3     | Realization of 4-bit parallel adder/subtractions using    | 14-18   |  |

|       | 7483 IC                                                   |         |  |

| 4     | Realization of 3-bit Binary to Gray code conversion       | 19-23   |  |

|       | and vice versa.                                           |         |  |

| 5     | MUX/DEMUX – use of 74153, 74139 for arithmetic            | 24-35   |  |

|       | circuits and code converter                               |         |  |

| 6     | MUX/DEMUX using Verilog HDL module                        | 36-39   |  |

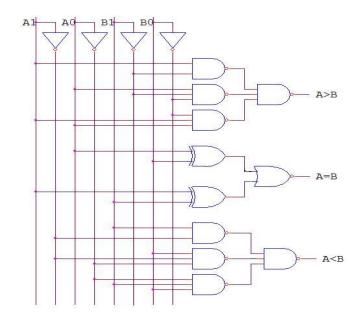

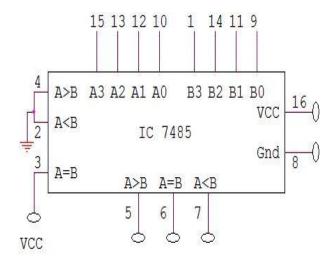

| 7     | Realization of One/Two/Four-bit                           | 40-44   |  |

|       | comparator/multiplier using gates ,7485 Ic and Verilog    |         |  |

|       | HDL module                                                |         |  |

| 8     | BCD to 7 Segment Decoder/Driver, Design of                | 45-55   |  |

|       | Encoder with & without priority (74147) and Verilog       |         |  |

|       | HDL module                                                |         |  |

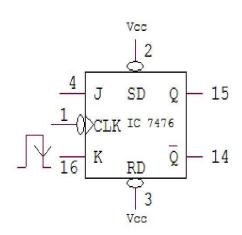

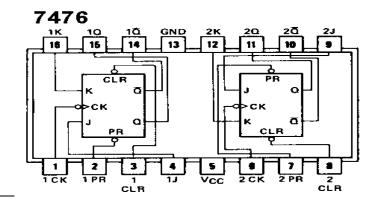

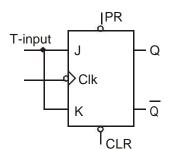

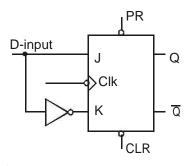

| 9     | Truth table verification of Flip-Flops: (i) JK Master     | 45-55   |  |

|       | slave (ii) T type and (iii) D type. Realization of 3 bit  |         |  |

|       | counters as a sequential circuit and MOD – N counter      |         |  |

|       | (7476)                                                    |         |  |

| 10    | Realization of 4 bit counters as a sequential circuit and | 56-63   |  |

|       | MOD – N counter design                                    |         |  |

|       | (7490, 74192) and using Verilog HDL module                |         |  |

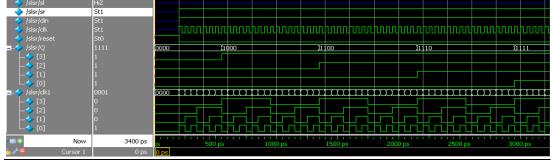

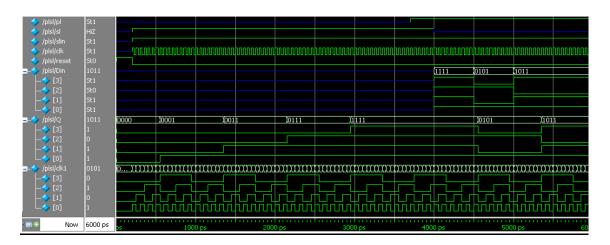

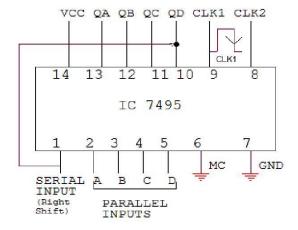

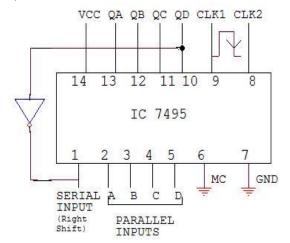

| 11    | Shift left, shift right, SIPO, SISO, PISO, PIPO           | 64-68   |  |

|       | operations using 74S95 and using Verilog HDL              |         |  |

|       | module                                                    |         |  |

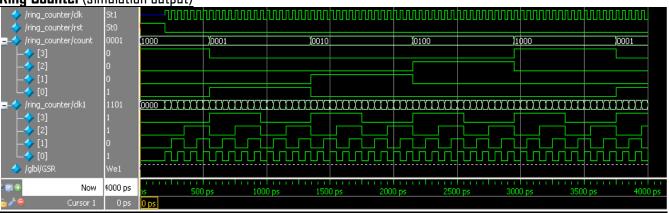

| 12    | Writing the Verilog module to simulate and synthesize     | 69-72   |  |

|       | Ring/Johnson Counter and using Verilog HDL module         |         |  |

| 13    | Writing a Verilog module to interface Stepper motor       | 73-76   |  |

|       | and DC-motor to FPGA.                                     |         |  |

| 14    | Writing a Verilog module to interface DAC to FPGA.        | 73-76   |  |

# **TEXT BOOKS**

- 1. John M Yarbrough, "Digital Logic Applications and Design", Thomson Learning, 2001.

- 2. Donald D Givone, "Digital Principles and Design", Tata McGraw Hill Edition, 2002.

- 3. Samir Palnitkar, VERILOG HDL-A Guide to digital design and synthesis- 2nd edition, Pearson education.2003.

- 4. Wayne Wolf, FPGA based system design- Reprint 2005, Pearson Education.

# **REFERENCE BOOKS:**

- 1. R D Sudhaker Samuel, "Logic Design A simplified approach", Sanguine Technical Publishers, 2004.

- 2. Stephen Brown, Zvonko Vranesic, Fundamentals of Digital logic with VERILOG design, TMH.

# WEB LINKS AND VIDEO LECTURES (e-Resources):

- https://dld-iitb.vlabs.ac.in

- https://de-iitr.vlabs.ac.in

- https://de-iitg.vlabs.ac.in

- http://vlabs.iitkgp.ac.in

# **Course Contents and Lecture Schedule:**

| Lesso<br>n<br>Plan | Topics                                                                                                      | Durati<br>on | CO's  |

|--------------------|-------------------------------------------------------------------------------------------------------------|--------------|-------|

|                    |                                                                                                             |              |       |

| 1                  | Simplification, realization of Boolean expressions using logic gates/Universal gates and Verilog HDL module | 2 hr         | CO1,3 |

| 2                  | Realization of Half/Full adder and Half/Full subtractions using logic gates and Verilog HDL module          | 2 hr         | CO1,3 |

| 3                  | Realization of 4-bit parallel adder/subtractions using 7483 IC                                              | 2 hr         | CO1,3 |

| 4                  | Realization of 3-bit Binary to Gray code conversion and vice versa.                                         | 2 hr         | CO1,3 |

| 5                  | MUX/DEMUX – use of 74153, 74139 for arithmetic circuits and code converter                                  | 2 hr         | CO1   |

| 6                  | MUX/DEMUX using Verilog HDL module                                                                          | 2 hr         | CO1,3 |

| 7                  | Realization of One/Two/Four-bit comparator/multiplier using gates ,7485 Ic and Verilog HDL module           | 2 hr         | CO1,3 |

| 8  | BCD to 7 Segment Decoder/Driver , Design of Encoder with & without priority (74147) and Verilog HDL module                                                                 | 2 hr | CO2,4 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|

| 9  | Truth table verification of Flip-Flops: (i) JK Master slave (ii) T type and (iii) D type. Realization of 3 bit counters as a sequential circuit and MOD – N counter (7476) | 2 hr | CO2,4 |

| 10 | Realization of 4 bit counters as a sequential circuit and MOD – N counter design (7490, 74192) and using Verilog HDL module                                                | 2 hr | CO2,4 |

| 11 | Shift left, shift right, SIPO, SISO, PISO, PIPO operations using 74S95 and using Verilog HDL module                                                                        | 2 hr | CO2,4 |

| 12 | Writing the Verilog module to simulate and synthesize Ring/Johnson Counter and using Verilog HDL module                                                                    | 2 hr | CO2,4 |

| 13 | Writing a Verilog module to interface Stepper motor and DC-motor to FPGA                                                                                                   | 2 hr | CO4,5 |

| 14 | Writing a Verilog module to interface DAC to FPGA.                                                                                                                         | 2 hr | CO4,5 |

# **Course Outcomes**

- 1. Ability to design and evaluate combinational logic circuits with minimum gates. (PO1, 2, 3, 8,9, 10, 12) (PSO1, 2, 3)

- 2. Ability to design and evaluate sequential networks with a minimum number of gates. (PO1, 2, 3,8,9,1012) (PSO 1, 2, 3)

- 3. Ability to design and evaluate simple or complex logical circuits using Verilog HDL. (PO1, 2, 3, , 8,9, 10, 12) (PSO1, 2, 3)

- 4. Ability to design & evaluate memory blocks with minimum number of gates using FPGA architecture. (PO1, 2, 3, , 8,9,10, 12) (PSO 1, 2, 3).

- 5. Design and synthesize digital circuit on FPGA processor using EDA tools. (PO1, 2, 3, , 8, 9, 10, 12) (PSO1, 2, 3)

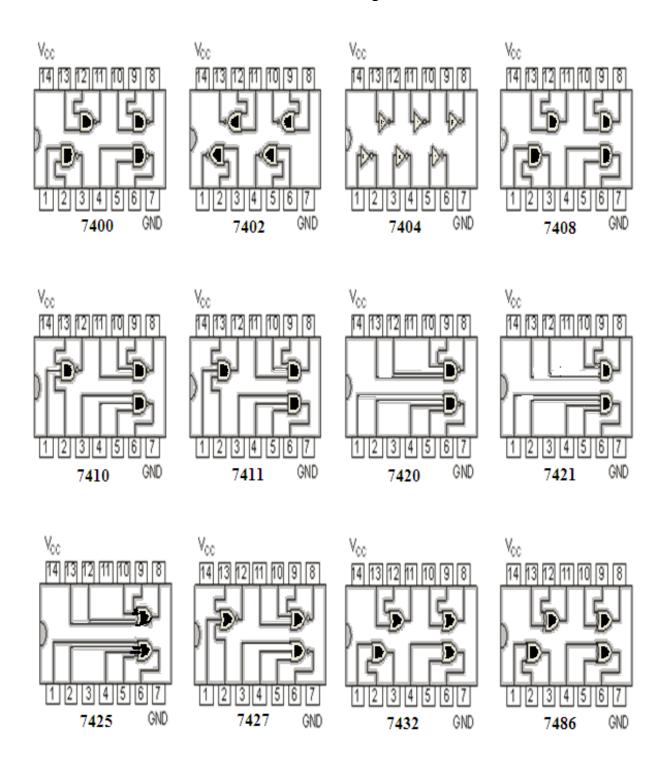

# **IC Internal Pin Configuration:**

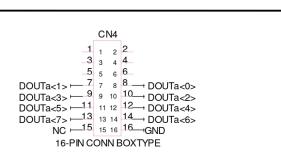

# Pin Details of 3S400 Deta Sheet

# 2. INPUT DIP SWITCHES

There are 4 DIP (DIP1 to DIP4) switches provided on the baseboard which are connected to 32 input LEDs (LG1 to LG32) and to the connectors connecting the Daughter Board. DIP switches are represented on baseboard from DIP1 through DIP4. When the drag button of the dip switch is kept in the **ON** side, the input is high (1) the corresponding O/p LED will go **ON** and when the drag button of the dip switch is kept in the **OFF** side the input is low (0) and the corresponding O/p LED will go **OFF**.

**DIP1 (1)** to **DIP1 (8)** are represented as **IN1** to **IN8**, **DIP2 (1)** to **DIP2 (8)** are represented as **IN9** to **IN16**, **DIP3 (1)** and **DIP3 (8)** are represented as **IN17** to **IN24** & **DIP4 (1)** and **DIP4 (8)** are represented as **IN25** to **IN32** respectively. If IN1 is ON LED LG1 will be ON otherwise LG1 will be OFF and so on.

# **PIN DETAILS**

| UCF       | Connector pin | 3S50           | 3S400          | XC9572  |

|-----------|---------------|----------------|----------------|---------|

| UCF       | Connector pin | <b>IC Pins</b> | <b>IC Pins</b> | IC Pins |

| INPUT<0>  | CN9/20        | P21            | P21            | P31     |

| INPUT<1>  | CN9/22        | P27            | P27            | P33     |

| INPUT<2>  | CN9/24        | P29            | P29            | P35     |

| INPUT<3>  | CN9/26        | P35            | P35            | P37     |

| INPUT<4>  | CN9/28        | P37            | P37            | P40     |

| INPUT<5>  | CN9/30        | P40            | P40            | P43     |

| INPUT<6>  | CN9/32        | P43            | P43            | P45     |

| INPUT<7>  | CN9/34        | P45            | P45            | P47     |

| INPUT<8>  | CN9/36        | P48            | P48            | P50     |

| INPUT<9>  | CN9/38        | P52            | P52            | P52     |

| INPUT<10> | CN10/6        | P58            | P58            | P54     |

| INPUT<11> | CN10/8        | P62            | P62            | P56     |

| INPUT<12> | CN10/10       | P64            | P64            | NA      |

| INPUT<13> | CN10/12       | P67            | P67            | NA      |

| INPUT<14> | CN10/14       | P71            | P71            | NA      |

| INPUT<15> | CN10/16       | P74            | P74            | NA      |

| INPUT<16> | CN10/24       | P80            | P80            | NA      |

| INPUT<17> | CN11/37       | P162           | P162           | NA      |

| INPUT<18> | CN10/28       | P86            | P86            | NA      |

| INPUT<19> | CN10/30       | P90            | P90            | NA      |

| INPUT<20> | CN10/32       | P94            | P94            | NA      |

| INPUT<21> | CN10/34       | P100           | P100           | NA      |

| INPUT<22> | CN10/36       | P102           | P102           | NA      |

| INPUT<23> | CN11/4        | P107           | P107           | NA      |

| INPUT<24> | CN11/6        | P113           | P113           | NA      |

| INPUT<25> | CN11/8        | P115           | P115           | NA      |

| INPUT<26> | CN11/10       | P117           | P117           | NA      |

| INPUT<27> | CN11/12       | P120           | P120           | NA      |

| INPUT<28> | CN11/14       | P123           | P123           | NA      |

| INPUT<29> | CN11/16       | P125           | P125           | NA      |

| INPUT<30> | CN11/18       | P131           | P131           | NA      |

| INPUT<31> | CN11/20       | P133           | P133           | NA      |

# **Output LEDs**

There are 32 O/P LEDs (LR1 to LR32) which are connected to FPGA/CPLD output pins. These LEDs are active high type, i.e., they switch ON to indicate a logical '1' status.

# **PIN DETAILS**

| UCF        | Connector | 3S50    | 3S400   | XC9572  |

|------------|-----------|---------|---------|---------|

| oci        | PIN       | IC pins | IC pins | IC pins |

| OUTPUT<0>  | CN9/19    | P20     | P20     | P26     |

| OUTPUT<1>  | CN9/21    | P26     | P26     | P32     |

| OUTPUT<2>  | CN9/23    | P28     | P28     | P34     |

| OUTPUT<3>  | CN9/25    | P34     | P34     | P36     |

| OUTPUT<4>  | CN9/27    | P36     | P36     | P39     |

| OUTPUT<5>  | CN9/29    | P39     | P39     | P41     |

| OUTPUT<6>  | CN9/31    | P42     | P42     | P44     |

| OUTPUT<7>  | CN9/33    | P44     | P44     | P46     |

| OUTPUT<8>  | CN9/35    | P46     | P46     | P48     |

| OUTPUT<9>  | CN9/37    | P51     | P51     | P51     |

| OUTPUT<10> | CN10/5    | P57     | P57     | P53     |

| OUTPUT<11> | CN10/7    | P61     | P61     | P55     |

| OUTPUT<12> | CN10/9    | P63     | P63     | NA      |

| OUTPUT<13> | CN10/11   | P65     | P65     | NA      |

| OUTPUT<14> | CN10/13   | P68     | P68     | NA      |

| OUTPUT<15> | CN10/15   | P72     | P72     | NA      |

| OUTPUT<16> | CN10/23   | P78     | P78     | NA      |

| OUTPUT<17> | CN10/25   | P81     | P81     | NA      |

| OUTPUT<18> | CN10/27   | P85     | P85     | NA      |

| OUTPUT<19> | CN10/29   | P87     | P87     | NA      |

| OUTPUT<20> | CN10/31   | P93     | P93     | NA      |

| OUTPUT<21> | CN10/33   | P95     | P95     | NA      |

| OUTPUT<22> | CN10/35   | P101    | P101    | NA      |

| OUTPUT<23> | CN11/3    | P106    | P106    | NA      |

| OUTPUT<24> | CN11/5    | P111    | P111    | NA      |

| OUTPUT<25> | CN11/7    | P114    | P114    | NA      |

| OUTPUT<26> | CN11/9    | P116    | P116    | NA      |

| OUTPUT<27> | CN11/11   | P119    | P119    | NA      |

| OUTPUT<28> | CN11/13   | P122    | P122    | NA      |

| OUTPUT<29> | CN11/15   | P124    | P124    | NA      |

| OUTPUT<30> | CN11/17   | P130    | P130    | NA      |

| OUTPUT<31> | CN11/19   | P132    | P132    | NA      |

NOTE: Download sw\_led\_test.bit/jed files for FPGA/CPLD

CONNECTIONS: Connect 26 pin FRC cable between J1 to J3 on SPARTAN6 DB.

**RESULT:** DIP1 to DIP4 are input pins & LR1 to LR32 used to see the corresponding output in LEDs.

#### 6. SPEED & DIRECTION CONTROL OF DC MOTOR

PWM method is used to run the DC motor. First 3 pins of DIP1are used to control the speed of the DC motor Switch (SW5) is used to control the direction of DC motor. DC motor should be connected to the 2-pin Relimate connector RM2.

CONNECTIONS: Connect 10 pin FRC cable from CN22 to CN24.

Connect 26 pin FRC cable between J1 to J2 on SPARTAN6 DB.

#### **PINDETAILS**

| UCF    | Connector pin | 3S50<br>IC PINs | 3S400<br>IC PINs | XC9572<br>IC PINS |

|--------|---------------|-----------------|------------------|-------------------|

| CLK    | CN10/18       | P79             | P79              | P9                |

| PDCM   | CN12/35       | P203            | P203             | P10               |

| PSW<0> | CN9/20        | P21             | P21              | P31               |

| PSW<1> | CN9/22        | P27             | P27              | P33               |

| PSW<2> | CN9/24        | P29             | P29              | P35               |

#### NOTE: Download dc\_motor.bit/jed files for FPGA/CPLD

**RESULT:** connect the DC motor to relaymate connector RM2 & by selecting the above explained switches we can vary the speed of DC motor & to change the direction of rotation of DC motor use switch SW5.

#### 7. SPEED & DIRECTION CONTROL OF STEPPER MOTOR

Note: "We can run a Stepper motor which draws up to 300mA current.

Caution: "If it draws the current more than 300mA, the U1 IC will get heated".

Stepper motor can be interfaced directly to the power-mate connector PM1. Direction of the stepper motor can be changed by changing the DIP1 pin 1.Speed of the stepper motor can be controlled through the software by changing the counter value.

**CONNECTIONS:** Connect 10 pin FRC cable from CN22 to CN24.

Connect 26 pin FRC cable between J1 to J2 on SPARTAN6 DB.

## **PIN DETAILS**

| UCF     | Connector<br>pin | 3S50<br>IC PIN |      | XC9572<br>IC PINS |

|---------|------------------|----------------|------|-------------------|

| CLK     | CN10/18          | P79            | P79  | P9                |

| CNTRL   | CN9/20           | P21            | P21  | P31               |

| DOUT<0> | CN12/14          | P169           | P169 | P69               |

| DOUT<1> | CN12/17          | P175           | P175 | P72               |

| DOUT<2> | CN12/18          | P176           | P176 | P74               |

| DOUT<3> | CN12/19          | P178           | P178 | P75               |

Connection details of the power-mate connector PM1 are as follows:

| Signal  | PM1   |

|---------|-------|

| VCC     | PIN 1 |

| DOUT<3> | PIN 2 |

| DOUT<2> | PIN 3 |

| DOUT<1> | PIN 4 |

| DOUT<0> | PIN 5 |

## NOTE: Download stepper\_motor.bit/jed files for FPGA/CPLD

**RESULT:** connect the stepper motor to powermate connector PM1 & by selecting the switch DIP1/pin1 we can change the direction of rotation of stepper motor.

Advanced

Systems

Electronic

ALS/SDA/FPGA-04/LM

## **PIN Details**

| UCF    | CONNECTOR | XC3S50  | XC3S400 | XC9572 |

|--------|-----------|---------|---------|--------|

|        | PINS      | IC PIN  | IC PIN  | IC PIN |

| CLKIN  | CN10/18   | PIN 79  | PIN 79  | PIN 9  |

| DOUTA0 | CN12/26   | PIN 187 | PIN 187 | PIN 83 |

| DOUTA1 | CN12/25   | PIN 185 | PIN 185 | PIN 82 |

| DOUTA2 | CN12/28   | PIN 190 | PIN 190 | PIN 1  |

| DOUTA3 | CN12/27   | PIN 189 | PIN 189 | PIN 84 |

| DOUTA4 | CN12/30   | PIN 194 | PIN 194 | PIN 3  |

| DOUTA5 | CN12/29   | PIN 191 | PIN 191 | PIN 2  |

| DOUTA6 | CN12/32   | PIN 197 | PIN 197 | PIN 5  |

| DOUTA7 | CN12/31   | PIN 196 | PIN 196 | PIN 4  |

LAB MANUAL

#### NOTE:

- 1. Download dacsqr.bit/jed file for FPGA/CPLD for Square wave

- 2. Download dacsine.bit/jed file for FPGA/CPLD for Sine wave

- 3. Download dacramp.bit/jed file for FPGA/CPLD for Ramp wave

- 4. Download dactri.bit/jed file for FPGA/CPLD for Triangle wave

**RESULT:** Observe the sine, square, ramp & triangular waves on CRO. Jumper JP4 is provided for UNI polar or Bi polar output.

### 11. ELEVATOR INTERFACE

## **OPERATION:**

There are 4 keys on the interface board, which are used to send a request for the elevator. Each key is associated with one floor. Key request is acknowledged by a Red LED, which is a part of the hardware of the interface board.

There are 10 LEDs L1 to L10. L1, L4, L7 and L10 are green LEDs corresponding to the floor. Remaining 6 LEDS are amber in color, which indicate the shift position. The software generates a 4-bit code to switch on these LEDs. Whenever a key (SW1 to SW4) is pressed,

15 of 75

REV2.0

# EXPERIMENT: 1 REALIZATION AND VERIFICATION OF LOGIC GATES

AIM: To study and verify the truth table of logic gates

| LEARNING OBJECTIVE:                             |

|-------------------------------------------------|

| ☐ Identify various ICs and their specification. |

| •                                               |

| COMPONENTS REQUIRED:                            |

| ☐ Logic gates (IC) trainer kit.                 |

| ☐ Connecting patch chords.                      |

□ IC 7400, IC 7402, IC 7404, IC 7408, IC 7432, IC 7486.

# THEORY:

The basic logic gates are the building blocks of more complex logic circuits. These logic gates perform the basic Boolean functions, such as AND, OR, NAND, NOR, Inversion, Exclusive-OR, Exclusive-NOR. Fig. below shows the circuit symbol, Boolean function, and truth. It is seen from the Fig that each gate has one or two binary inputs, A and B, and one binary output, C. The small circle on the output of the circuit symbols designates the logic complement. The AND, OR, NAND, and NOR gates can be extended to have more than two inputs. A gate can be extended to have multiple inputs if the binary operation it represents is commutative and associative.

These basic logic gates are implemented as small-scale integrated circuits (SSICs) or as part of more complex medium scale (MSI) or very large-scale (VLSI) integrated circuits. Digital IC gates are classified not only by their logic operation, but also the specific logic-circuit family to which they belong. Each logic family has its own basic electronic circuit upon which more complex digital circuits and functions are developed. The following logic families are the most frequently used.

TTL Transistor-transistor logic ECL Emitter-coupled logic

MOS Metal-oxide semiconductor

CMOS Complementary metal-oxide semiconductor

TTL and ECL are based upon bipolar transistors. TTL has a well-established popularity among logic families. ECL is used only in systems requiring high-speed operation. MOS and CMOS, are based on field effect transistors. They are widely used in large scale integrated circuits because of their high component density and relatively low power consumption. CMOS logic consumes far less power than MOS logic. There are various commercial integrated circuit chips available. TTL ICs are usually distinguished by numerical designation as the 5400 and 7400 series

## PROCEDURE:

- 1. Check the components for their working.

- 2. Insert the appropriate IC into the IC base.

- 3. Make connections as shown in the circuit diagram.

- 4 Provide the input data via the input switches and observe the output on output LEDs

| S.NO | GATE     | SYMBOL                                              | INPU | TS  | OUTPUT |

|------|----------|-----------------------------------------------------|------|-----|--------|

|      |          |                                                     | A    | В   | C      |

| 1.   | NAND IC  |                                                     | 0    | 0   | 1      |

|      | 7400     | $A = C = \overline{A}\overline{B}$                  | 0    | 1   | 1      |

|      |          | В                                                   | 1    | 0   | 1      |

|      | 1        | 90°                                                 | 1    | 1   | 0      |

| 2.   | NOR IC   |                                                     | 0    | 0   | 1      |

|      | 7402     | $A \longrightarrow C = \overline{A} + \overline{B}$ | 0    | 1   | 0      |

|      |          | В                                                   | 1    | 0   | 0      |

|      |          |                                                     | 1    | 1   | 0      |

| 3.   | AND IC   |                                                     | 0    | 0   | 0      |

|      | 7408     | AC=AB                                               | 0    | 1   | 0      |

|      |          | В                                                   | 1    | 0   | 0      |

|      |          |                                                     | 1    | 1   | 1      |

| 4.   | OR       | 200                                                 | 0    | 0   | 0      |

|      | IC 7432  | A—————————————————————————————————————              | 0    | 1   | 1      |

|      |          | В——                                                 | 1    | 0   | 1      |

|      |          |                                                     | 1    | 1   | 1      |

| 5.   | NOT      | AC= \( \overline{A} \)                              | 1    | (*) | 0      |

|      | IC 7404  |                                                     | 0    | 120 | 1      |

| 6.   | EX-OR IC |                                                     | 0    | 0   | 0      |

|      | 7486     | A                                                   | 0    | 1   | 1      |

|      |          | 1) 1                                                | 1    | 0   | 1      |

|      |          | B C=AB+BA                                           | 1    | 1   | 0      |

# **VIVA QUESTIONS:**

Why NAND & NOR gates are called universal gates?

Realize the EX – OR gates using minimum number of NAND gates.

Give the truth table for EX-NOR and realize using NAND gates?

What are the logic low and High levels of TTL IC's and CMOS IC's?

Compare TTL logic family with CMOS family?

Which logic family is fastest and which has low power dissipation?

# **REALIZATION OF A BOOLEAN FUNCTION.**

<u>AIM:</u> To simplify the given expression and to realize it using Basic gates and Universal gates

# LEARNING OBJECTIVE:

To simplify the Boolean expression and to build the logic circuit.

Given a Truth table to derive the Boolean expressions and build the logic circuit to realize it.

# **COMPONENTS REQUIRED:**

IC 7400, IC 7408, IC 7432, IC 7406, IC 7402, Patch Cords & IC Trainer Kit.

# THEORY:

Canonical Forms (Normal Forms): Any Boolean function can be written in disjunctive normal form (sum of min-terms) or conjunctive normal form (product of max-terms).

A Boolean function can be represented by a Karnaugh map in which each cell corresponds to a minterm. The cells are arranged in such a way that any two immediately adjacent cells correspond to two minterms of distance 1. There is more than one way to construct a map with this property.

# Karnaugh Maps

For a function of two variables, say, f(x, y),

|    | X'     | X      |

|----|--------|--------|

| y' | f(0,0) | f(1,0) |

| У  | f(0,1) | f(1,1) |

For a function of three variables, say, f(x, y, z)

|    | x'y'     | x'y      | xy       | xy'      |

|----|----------|----------|----------|----------|

| z' | f(0,0,0) | f(0,1,0) | f(1,1,0) | f(1,0,0) |

| z  | f(0,0,1) | f(0,1,1) | f(1,1,1) | f(1,0,1) |

For a function of four variables: f(w, x, y, z

|      | w'x' | w'x | WX | WX' |

|------|------|-----|----|-----|

| y'z' | 0    | 4   | 12 | 8   |

| y'z  | 1    | 5   | 13 | 9   |

| yz   | 3    | 7   | 15 | 11  |

| yz'  | 2    | 6   | 14 | 10  |

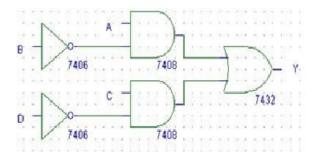

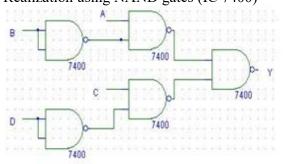

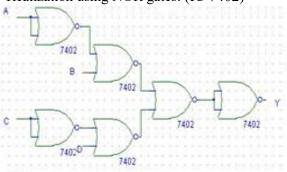

# Realization of Boolean expression:

1)

$$Y = \bar{A} \ \bar{B} \ C \ \bar{D} + \bar{A} \ B C \ \bar{D} + \bar{A} \ \bar{B} \ \bar{C} \ \bar{D} + \bar{A}$$

After simplifying using K-Map method we

$\bar{Y} = \bar{A} B + C D$

# get Realization using Basic gates

TRUTH TABLE

| A         B         C         D         Y           0         0         0         0         0           0         0         0         1         0           0         0         1         0         1           0         0         1         1         0           0         1         0         0         0           0         1         0         1         0           0         1         1         0         1           0         1         1         1         0           1         0         0         0         1 |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     0     0     1     0       0     0     1     0     1       0     0     1     1     0       0     1     0     0     0       0     1     0     1     0       0     1     1     0     1       0     1     1     1     0                                                                                                                                                                                                                                                                                                     |  |

| 0     0     1     0     1       0     0     1     1     0       0     1     0     0     0       0     1     0     1     0       0     1     1     0     1       0     1     1     1     0                                                                                                                                                                                                                                                                                                                                     |  |

| 0     0     1     1     0       0     1     0     0     0       0     1     0     1     0       0     1     1     0     1       0     1     1     1     0                                                                                                                                                                                                                                                                                                                                                                     |  |

| 0         1         0         0         0           0         1         0         1         0           0         1         1         0         1           0         1         1         1         0                                                                                                                                                                                                                                                                                                                         |  |

| 0         1         0         1         0           0         1         1         0         1           0         1         1         1         0                                                                                                                                                                                                                                                                                                                                                                             |  |

| 0 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0 1 1 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 1 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 1 0 0 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 1 0 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 1 0 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1 1 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 1 1 0 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 1 1 1 1 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

0

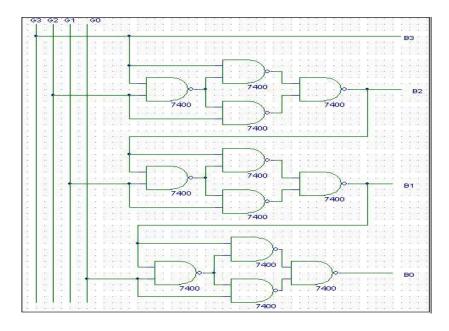

Realization using NAND gates (IC 7400)

Realization using NOR gates. (IC 7402)

2) For the given Truth Table, realize a logical circuit using basic gates and NAND gates

|     |   | Output |   |   |   |

|-----|---|--------|---|---|---|

| •   | A | В      | C | D | Y |

|     | 0 | 0      | 0 | 0 | 1 |

| •   | 0 | 0      | 0 | 1 | 1 |

|     | 0 | 0      | 1 | 0 | 0 |

|     | 0 | 0      | 1 | 1 | 0 |

|     | 0 | 1      | 0 | 0 | 1 |

|     | 0 | 1      | 0 | 1 | 1 |

|     | 0 | 1      | 1 | 0 | 0 |

|     | 0 | 1      | 1 | 1 | 0 |

|     | 1 | 0      | 0 | 0 | 0 |

|     | 1 | 0      | 0 | 1 | 0 |

|     | 1 | 0      | 1 | 0 | 0 |

|     | 1 | 0      | 1 | 1 | 0 |

|     | 1 | 1      | 0 | 0 | 0 |

| - · | 1 | 1      | 0 | 1 | 1 |

|     | 1 | 1      | 1 | 0 | 0 |

| - · | 1 | 1      | 1 | 1 | 1 |

# **PROCEDURE:**

Check the components for their working.

Insert the appropriate IC into the IC base.

Make connections as shown in the circuit diagram.

Provide the input data via the input switches and observe the output on output LEDs Verify the Truth Table

RESULT: Simplified and verified the Boolean function using basic gates and universal gates

# VIVA QUESTIONS:

- 1) What are the different methods to obtain minimal expression?

- 2) What is a Min term and Max term

- 3) State the difference between SOP and POS.

- 4) What is meant by canonical representation?

- 5) What is K-map? Why is it used?

- 6) What are universal gates?

# VERILOG MODULE FOR BASIC GATES (DATA FLOW)

```

module basic_gates(input a, input b, output [7:0]y);

assign y[0] = a & b;

assign y[1] = ~(a & b);

assign y[2] = a | b;

assign y[3] = ~(a | b);

assign y[4] = a ^ b;

assign y[5] = ~(a ^ b);

assign y[6] = ~ a;

assign y[7] = ~ b;

endmodule

```

# BASIC GATES (GATE LEVEL)

```

module basic_gates(input a, input b, output [7:0]y);

and a1(y[0], a,b);

nand a2(y[1], a, b);

or a3(y[2], a, b);

nor a4(y[3], a, b);

xor a5(y[4], a, b);

xnor a6(y[5], a, b);

not a7(y[6], a);

not a8(y[7], b);

endmodule

```

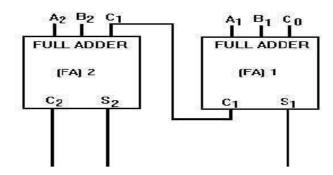

# **EXPERIMENT: 2**

# ADDERS AND SUBTRACTORS

# AIM: To realize

- i) Half Adder and Full Adder

- ii) Half subtraction and Full Subtraction by using Basic gates and NAND gates

# LEARNING OBJECTIVE:

To realize the adder and subtraction circuits using basic gates and universal gates to realize full adder using two half adders

To realize a full subtraction using two half subtractions

# **COMPONENTS REQUIRED:**

IC 7400, IC 7408, IC 7486, IC 7432, Patch Cords & IC Trainer Kit.

# THEORY:

*Half-Adder:* A combinational logic circuit that performs the addition of two data bits, A and B, is called a half-adder. Addition will result in two output bits; one of which is the sum bit, S, and the other is the carry bit, C. The Boolean functions describing the half-adder are:

$$S = A \oplus B$$

$C = A B$

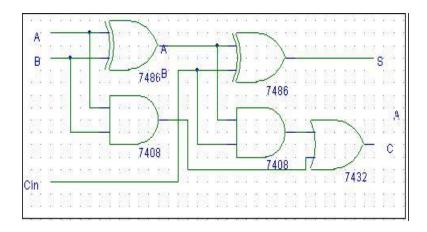

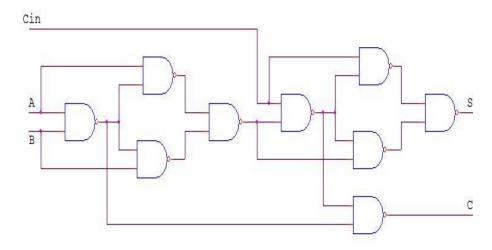

Full-Adder: The half-adder does not take the carry bit from its previous stage into account. This carry bit from its previous stage is called carry-in bit. A combinational logic circuit that adds two data bits, A and B, and a carry-in bit, Cin, is called a full-adder. The Boolean functions describing the full-adder are:

$$S = (x \oplus y) \oplus Cin$$

$C = xy + Cin(x \oplus y)$

Half Subtractor: Subtracting a single-bit binary value B from another A (i.e. A -B) produces a difference bit D and a borrow out bit B-out. This operation is called half subtraction and the circuit to realize it is called a half subtractor. The Boolean functions describing the half-Subtractor are:

$$S = A \oplus B$$

$C = A'B$

*Full Subtractor:* Subtracting two single-bit binary values, B, Cin from a single-bit value A produces a difference bit D and a borrow out Br bit. This is called full subtraction. The Boolean functions describing the full-subtracter are:

$$D = (x \oplus y) \oplus Cin$$

Br= A'B + A'(Cin) + B(Cin)

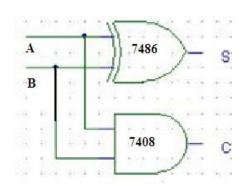

# I. TO REALIZE HALF ADDER

# TRUTH TABLE

| INPUTS |   | OUT | PUTS |

|--------|---|-----|------|

| A      | В | S   | C    |

| 0      | 0 | 0   | 0    |

| 0      | 1 | 1   | 0    |

| 1      | 0 | 1   | 0    |

| 1      | 1 | 0   | 1    |

# **BOOLEAN EXPRESSIONS:**

$S=A \oplus B$ C=A B

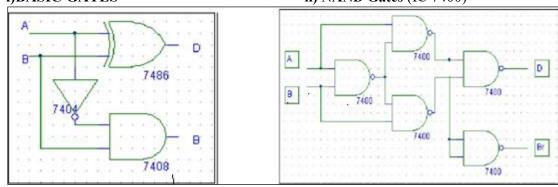

# i) Basic Gates

# ii) NAND Gates

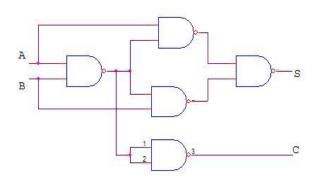

# II. FULL ADDER

**TRUTH TABLE**

| П | NPUT | OUT | PUTS |   |

|---|------|-----|------|---|

| A | В    | Cin | S    | C |

| 0 | 0    | 0   | 0    | 0 |

| 0 | 0    | 1   | 1    | 0 |

| 0 | 1    | 0   | 1    | 0 |

| 0 | 1    | 1   | 0    | 1 |

| 1 | 0    | 0   | 1    | 0 |

| 1 | 0    | 1   | 0    | 1 |

| 1 | 1    | 0   | 0    | 1 |

| 1 | 1    | 1   | 1    | 1 |

module ha2(input a,

input b, output sum,

output carry);

xor a1( sum, a,

b);

and a2( carry,

a, b);

endmodule

# **BOOLEAN EXPRESSIONS:**

$S=A \oplus B \oplus C$

C=A B + B Cin + A Cin

# i)BASIC GATES

# ii) NAND GATES. (IC 7400)

# III. HALF SUBTRACTOR

# TRUTH TABLE

| INPUTS |   | OUTPUTS |    |  |

|--------|---|---------|----|--|

| A      | В | D       | Br |  |

| 0      | 0 | 0       | 0  |  |

| 0      | 1 | 1       | 1  |  |

| 1      | 0 | 1       | 0  |  |

| 1      | 1 | 0       | 0  |  |

# **BOOLEAN EXPRESSIONS:**

$$\mathbf{D} = \mathbf{A} \oplus \mathbf{B}$$

$$\mathbf{Br} = \bar{AB}$$

# i)BASIC GATES

# ii) NAND Gates (IC 7400)

# IV. FULL SUBTRACTOR

# TRUTH TABLE

| II | NPUT | OUT | PUTS |    |

|----|------|-----|------|----|

| A  | В    | Cin | D    | Br |

| 0  | 0    | 0   | 0    | 0  |

| 0  | 0    | 1   | 1    | 1  |

| 0  | 1    | 0   | 1    | 1  |

| 0  | 1    | 1   | 0    | 1  |

| 1  | 0    | 0   | 1    | 0  |

| 1  | 0    | 1   | 0    | 0  |

| 1  | 1    | 0   | 0    | 0  |

| 1  | 1    | 1   | 1    | 1  |

# **BOOLEAN EXPRESSIONS:**

$$\mathbf{D} = \mathbf{A} \oplus \mathbf{B} \oplus \mathbf{C}$$

$$\mathbf{B} = \bar{A} \mathbf{B} + \mathbf{B} \mathbf{Cin} + \bar{A} \mathbf{Cin}$$

# i) BASIC GATES

#

# ii) To Realize the Full subtractor using NAND Gates only. (IC 7400)

module fulladder(a,b,c, sum,carry);

input a,b,c;

output sum, carry;

assign sum=a^b^c;

assign carry=(a&b)|(b&c)|(a&c);

endmodule

# PROCEDURE:

- ☐ Check the components for their working.

- ☐ Insert the appropriate IC into the IC base.

- ☐ Make connections as shown in the circuit diagram.

- ☐ Verify the Truth Table and observe the outputs

<u>RESULT:</u> The truth table of the above circuits is

verified.

# □ VIVA QUESTIONS:

- 1) What is a half adder?

- 2) What is a full adder?

- 3) What are the applications of adders?

- 4) What is a half subtractor?

- 5) What is a full subtractor?

- 6) What are the applications of subtractors?

- 7) Obtain the minimal expression for above circuits.

- 8) Realize a full adder using two half adders

- 9) Realize a full subtractors using two half subtractors

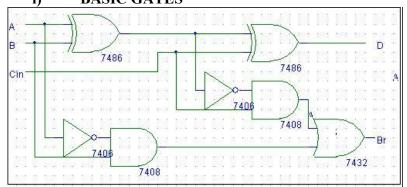

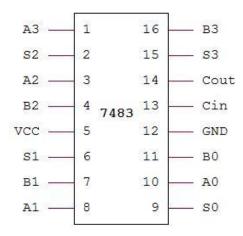

# **EXPERIMENT: 3**

# PARALLEL ADDER AND SUBTRACTOR

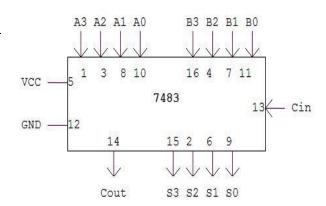

AIM: To design and set up the following circuit using IC 7483.

- i) A 4-bit binary parallel adder.

- ii) A 4-bit binary parallel subtractor.

## **LEARNING OBJECTIVE:**

To learn about IC 7483 and its internal structure. To realize a subtractor using adder IC 7483

## **COMPONENTS REQUIRED:**

IC 7483, IC 7486, Patch Cords & IC Trainer Kit.

# THEORY:

The Full adder can add single-digit binary numbers and carries. The largest sum that can be obtained using a full adder is 11<sub>2</sub>. Parallel adders can add multiple-digit numbers. If full adders are placed in parallel, we can add two- or four-digit numbers or any other size desired. Figure below uses STANDARD SYMBOLS to show a parallel adder capable of adding two, two-digit binary numbers The addend would be on A inputs, and the augend on the B inputs. For this explanation we will assume there is no input to C<sub>0</sub> (carry from a previous circuit)

To add 102 (addend) and 012 (augend), the addend inputs will be 1 on A2 and 0 on A1. The augend inputs will be 0 on B2 and 1 on B1. Working from right to left, as we do in normal addition, let's calculate the outputs of each full adder. With A1 at 0 and B1 at 1, the output of adder1 will be a sum (S1) of 1 with no carry (C1). Since A2 is 1 and B2 is 0, we have a sum (S2) of 1 with no carry (C2) from adder1. To determine the sum, read the outputs (C2, S2, and S1) from left to right. In this case, C2 = 0, S2 = 1, and S1 = 1. The sum, then, of 102 and 012

is 0112. To add four bits we require four full adders arranged in parallel. IC 7483 is a 4- bit parallel adder whose pin diagram is shown.

|        | MSB  |                  |                  |                  | LSB                 |

|--------|------|------------------|------------------|------------------|---------------------|

|        |      |                  |                  |                  | Cin                 |

| INPUTS | -    | A3               | A <sub>2</sub>   | A <sub>1</sub>   | $A_0$               |

|        |      | В <sub>3</sub> . | B <sub>2</sub> . | В <sub>1</sub> . | $\mathbf{B}_{_{0}}$ |

| OUTPUT | Cout | S <sub>3</sub>   | S <sub>2</sub>   | S <sub>1</sub>   | S <sub>0</sub>      |

IC 7483 pin diagram

# i) 4-Bit Binary Adder

An Example: 7+2=11 (1001)

7 is realized at A<sub>3</sub> A<sub>2</sub> A<sub>1</sub> A<sub>0</sub> = 0111  $\Box$  2 is realized at B<sub>3</sub> B<sub>2</sub> B<sub>1</sub> B<sub>0</sub> = 0010 Sum = 1001

# ADDER CIRCUIT:

### **PROCEDURE**:

- ☐ Check all the components for their working.

- ☐ Insert the appropriate IC into the IC base.

- ☐ Make connections as shown in the circuit diagram.

- ☐ Apply augend and addend bits on A and B and cin=0.

- ☐ Verify the results and observe the outputs.

#### ii) 4-BIT BINARY SUBTRACTOR.

Subtraction is carried out by adding 2's complement of the subtrahend.

Example: 8 - 3 = 5 (0101)

- □ 8 is realized at A<sub>3</sub> A<sub>2</sub> A<sub>1</sub> A<sub>0</sub> = 1000

- 3 is realized at B<sub>3</sub> B<sub>2</sub> B<sub>1</sub> B<sub>0</sub> through X-OR gates = 0011

- Output of X-OR gate is 1's complement of 3 = 1100

- ☐ 2's Complement can be obtained by adding Cin =1

#### Therefore

Cout

#### PROCEDURE:

- ☐ Check all the components for their working.

- ☐ Insert the appropriate IC into the IC base.

- ☐ Make connections as shown in the circuit diagram.

- □ Apply Minuend and subtrahend bits on A and B and cin=1.

- ☐ Verify the results and observe the outputs.

RESULTS: Verified the working of IC 7483 as adder and subtractor.

S3 S2 S1 S0

#### **VIVA QUESTIONS:**

- 1) What is the internal structure of 7483 IC?

- 2) What do you mean by code conversion?

- 3) What are the applications of code conversion?

- 4) How do you realize a subtractor using full adder?

- 5) What is a ripple Adder? What are its disadvantages?

Gray

G1

G0

## **EXPERIMENT: 4** BINARY TO GRAY CODE CONVERTER

**Binary**

B2 B1

**B3**

B0 G3

0 |

AIM: To realize Binary to Gray code converter and vice versa

#### LEARNING OBJECTIVE:

To learn the importance of non-weighted code

To learn to generate gray code

#### COMPONENTS REQUIRED:

IC 7400, IC 7486, and IC 7408, Patch Cords & IC Trainer Kit

| I) BINARY TO GRAY CONVERSION |

|------------------------------|

|------------------------------|

| 0 | 0 | 1 | 1 |

|---|---|---|---|

| 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 |

G3 = B3

$G2 = B3 \oplus B2$

| 0  | 1 | 1 | 0 |

|----|---|---|---|

| 0  | 1 | 1 | 0 |

| 1  | 0 | 0 | T |

| 1) | 0 | 0 | 1 |

G1=B1 ⊕

| 1         1         1         1           0         0         0         0 | 0 | 0 | 0 | 0 |

|---------------------------------------------------------------------------|---|---|---|---|

| 0 0 0 0                                                                   | 1 | 1 | 1 | 1 |

|                                                                           | 0 | 0 | 0 | 0 |

|                                                                           | 1 | 1 | 1 | 1 |

B2

G0=B1 ⊕ B0

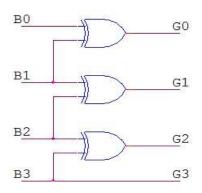

#### BINARY TO GRAY CODE USING EX-OR GATES

BOOLEAN EXPRESSIONS:

G3=B3  $G2=B3 \oplus B2$

G1=B1 ⊕ B2

G0=B1 ⊕ B0

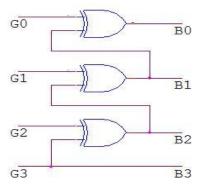

## REALIZATION USING NAND GATES: (IC 7400)

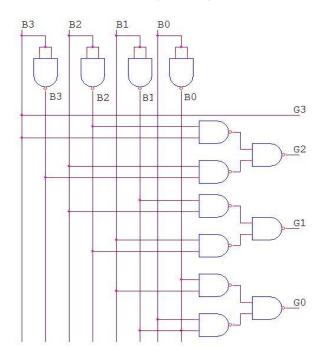

## II) GRAY TO BINARY CONVERSION

| 0  | 0 | 1 | 1 |

|----|---|---|---|

| 0  | 0 | 1 | 1 |

| 0  | 0 | 1 | 1 |

| .0 | 0 | 1 | 1 |

B3 = G3

.

| 0 | 1 | 0 | 1 |

|---|---|---|---|

| 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 |

|---|---|---|---|

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 |

$$B1 = G3 \oplus G2 \oplus G1$$

| 0 | 1 | 0 | 1 |

|---|---|---|---|

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

|    | Gray |    |    |    | Bina | ry |    |

|----|------|----|----|----|------|----|----|

| G3 | G2   | Gl | G0 | В3 | B2   | B1 | B0 |

| 0  | 0    | 0  | 0  | 0  | 0    | 0  | 0  |

| 0  | 0    | 0  | 1  | 0  | 0    | 0  | 1  |

| 0  | 0    | 1  | 1  | 0  | 0    | 1  | 0  |

| 0  | 0    | 1  | 0  | 0  | 0    | 1  | 1  |

| 0  | 1    | 1  | 0  | 0  | 1    | 0  | 0  |

| 0  | 1    | 1  | 1  | 0  | 1    | 0  | 1  |

| 0  | 1    | 0  | 1  | 0  | 1    | 1  | 0  |

| 0  | 1    | 0  | 0  | 0  | 1    | 1  | 1  |

| 1  | 1    | 0  | 0  | 1  | 0    | 0  | 0  |

| 1  | 1    | 0  | 1  | 1  | 0    | 0  | 1  |

| 1  | 1    | 1  | 1  | 1  | 0    | 1  | 0  |

| 1  | 1    | 1  | 0  | 1  | 0    | 1  | 1  |

| 1  | 0    | 1  | 0  | 1  | 1    | 0  | 0  |

| 1  | 0    | 1  | 1  | 1  | 1    | 0  | 1  |

| 1  | 0    | 0  | 1  | 1  | 1    | 1  | 0  |

| 1  | 0    | 0  | 0  | 1  | 1    | 1  | 1  |

#### **BOOLEAN EXPRESSIONS:**

B3=G3

B2=G3 ⊕ G2

$B1=G3 \oplus G2 \oplus G1$

$B0=G3 \oplus G2 \oplus G1 \oplus G0$

GRAY TO BINARY CODE CONVERSION USING EX-OR GATE

#### REALIZATION USING NAND GATES: (IC 7400)

## PROCEDURE:

- ☐ Check all the components for their working.

- ☐ Insert the appropriate IC into the IC base.

- ☐ Make connections as shown in the circuit diagram.

- ☐ Verify the Truth Table and observe the outputs.

<u>RESULT:</u> Binary to gray code conversion and vice versa is realized using EX-OR gates and NAND gates.

```

module btog(b, g);

input [3:0] b;

output [3:0] g;

assign g[0]=b[1]^b[0];

assign g[1]=b[2]^b[1];

assign g[2]=b[3]^b[2];

assign g[3]=b[3];

endmodule

```

#### VIVA QUESTIONS:

- 1) What are code converters?

- 2) What is the necessity of code conversions?

- 3) What is gray code?

- 4) Realize the Boolean expressions for

- a) Binary to gray code conversion

- b) Gray to binary code conversion

# EXPERIMENT: 5 MULTIPLEXER AND DEMULTIPLEXER

AIM: To design and set up the following circuit

- 1) To design and set up a 4:1 Multiplexer (MUX) using only NAND gates.

- 2) To design and set up a 1:4 Demultiplexer(DE-MUX) using only NAND gates.

- 3) To verify the various functions of IC 74153(MUX) and IC 74139(DEMUX).

- 4) To set up a Half/Full Adder and Half/Full Subtractor using IC 74153.

#### **LEARNING OBJECTIVE:**

To learn about various applications of multiplexer and de-multiplexer To learn and understand the working of IC 74153 and IC 74139

To learn to realize any function using Multiplexer

#### THEORY:

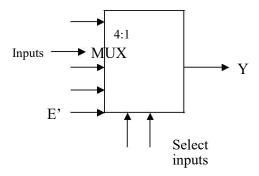

Multiplexers are very useful components in digital systems. They transfer a large number of information units over a smaller number of channels, (usually one channel) under the control of selection signals. Multiplexer means many to one. A multiplexer is a circuit with many inputs but only one output. By using control signals (select lines) we can select any input to the output. Multiplexer is also called as data selector because the output bit depends on the input data bit that is selected. The general multiplexer circuit has 2<sup>n</sup> input signals, n control/select signals and 1 output signal.

De-multiplexers perform the opposite function of multiplexers. They transfer a small number of information units (usually one unit) over a larger number of channels under the control of selection signals. The general de-multiplexer circuit has 1 input signal, n control/select signals and 2<sup>n</sup> output signals. De-multiplexer circuit can also be realized using a decoder circuit with enable.

#### **COMPONENTS REQUIRED:**

IC 7400, IC 7410, IC 7420, IC 7404, IC 74153, IC 74139, Patch Cords & IC Trainer Kit.

#### i) 4:1 MULTIPLEXER

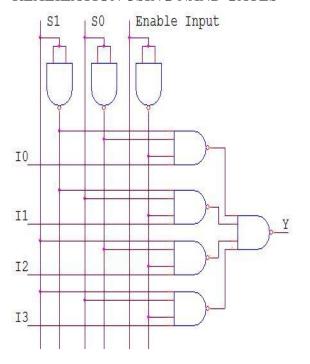

Output Y= E'S1'S0'I0 + E'S1'S0I1 + E'S1S0'I2 + E'S1S0I3

## REALIZATION USING NAND GATES

#### TRUTH TABLE

| Sel<br>Inp     | ect | Enable<br>Input |    | Inputs         |                |            | Out<br>puts |

|----------------|-----|-----------------|----|----------------|----------------|------------|-------------|

| S <sub>1</sub> | So  | E               | Io | I <sub>1</sub> | I <sub>2</sub> | <b>I</b> 3 | Y           |

| X              | X   | 1               | X  | X              | X              | X          | 0           |

| 0              | 0   | 0               | 0  | X              | X              | X          | 0           |

| 0              | 0   | 0               | 1  | X              | X              | X          | 1           |

| 0              | 1   | 0               | X  | 0              | X              | X          | 0           |

| 0              | 1   | 0               | X  | 1              | X              | X          | 1           |

| 1              | 0   | 0               | X  | X              | 0              | X          | 0           |

| 1              | 0   | 0               | X  | X              | 1              | X          | 1           |

| 1              | 1   | 0               | X  | X              | X              | 0          | 0           |

| 1              | 1   | 0               | X  | X              | X              | 1          | 1           |

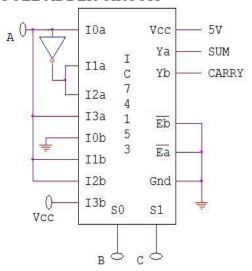

## **VERIFY IC 74153 MUX (DUAL 4:1 MULTIPLEXE**

## HALF ADDER USING MUX:

## **DESIGN:**

| SUM |    |  |

|-----|----|--|

| I0  | I1 |  |

| 0   | 1  |  |

| 2   | 3  |  |

| A   | A' |  |

| CARRY |    |  |  |

|-------|----|--|--|

| I0    | I1 |  |  |

| 0     | 1  |  |  |

| 2     | 3  |  |  |

| 0     | A  |  |  |

## TRUTH TABLE

| Inputs |   | Outputs |   |

|--------|---|---------|---|

| A      | В | S       | C |

| 0      | 0 | 0       | 0 |

| 0      | 1 | 1       | 0 |

| 1      | 0 | 1       | 0 |

| 1      | 1 | 0       | 1 |

## **FULL ADDER USING MUX:**

## **DESIGN:**

.

| A | 1 | A' | A' | A  |

|---|---|----|----|----|

| 4 | 1 | 5  | 6  | 7  |

| ( | ) | 1  | 2  | 3  |

| I | 0 | I1 | I3 | I3 |

| I0 | I1 | I3 | I3 |

|----|----|----|----|

| 0  | 1  | 2  | 3  |

| 4  | 5  | 6  | 7  |

| 0  | A  | A  | 1  |

#### TRUTH TABLE

|   | Inputs |   |   | puts |

|---|--------|---|---|------|

| A | В      | C | S | C    |

| 0 | 0      | 0 | 0 | 0    |

| 0 | 0      | 1 | 1 | 0    |

| 0 | 1      | 0 | 1 | 0    |

| 0 | 1      | 1 | 0 | 1    |

| 1 | 0      | 0 | 1 | 0    |

| 1 | 0      | 1 | 0 | 1    |

| 1 | 1      | 0 | 0 | 1    |

| 1 | 1      | 1 | 1 | 1    |

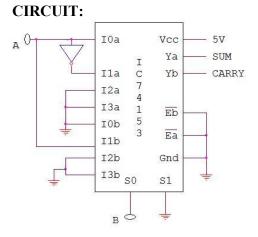

## FULL ADDER CIRCUIT

## HALF SUBTRACTOR USING MUX:

## DESIGN:

| D | <u> JIFFERENC</u> |    |  |  |

|---|-------------------|----|--|--|

|   | I0                | I1 |  |  |

|   | 0                 | 1  |  |  |

|   | 2                 | 3  |  |  |

|   | A                 | A' |  |  |

| ] | BORROW |    |  |  |

|---|--------|----|--|--|

|   | I0     | I1 |  |  |

|   | 0      | 1  |  |  |

|   | 2      | 3  |  |  |

|   | 0      | A' |  |  |

## CIRCUIT:

## TRUTH TABLE

| Inputs |   | Outputs |   |  |

|--------|---|---------|---|--|

| A      | В | D Br    |   |  |

| 0      | 0 | 0       | 0 |  |

| 0      | 1 | 1       | 1 |  |

| 1      | 0 | 1       | 0 |  |

| 1      | 1 | 0       | 0 |  |

#### **FULL SUBTRACTOR USING MUX:**

#### **DESIGN:**

#### DIFFERENCE

| Ι0 | I1 | I2 | I3 |

|----|----|----|----|

| 0  | 1  | 2  | 3  |

| 4  | 5  | 6  | 7  |

| A  | A' | A' | A  |

#### **BORROW**

| 10 | I1 | I2 | I3 |

|----|----|----|----|

| 0  | 1  | 2  | 3  |

| 4  | 5  | 6  | 7  |

| 0  | A' | A' | 1  |

#### TRUTH TABLE

|   | Inputs |   |   | puts |

|---|--------|---|---|------|

| A | В      | C | D | Br   |

| 0 | 0      | 0 | 0 | 0    |

| 0 | 0      | 1 | 1 | 1    |

| 0 | 1      | 0 | 1 | 1    |

| 0 | 1      | 1 | 0 | 1    |

| 1 | 0      | 0 | 1 | 0    |

| 1 | 0      | 1 | 0 | 0    |

| 1 | 1      | 0 | 0 | 0    |

| 1 | 1      | 1 | 1 | 1    |

#### **PROCEDURE:**

- ☐ Check all the components for their working.

- ☐ Insert the appropriate IC into the IC base.

- ☐ Make connections as shown in the circuit diagram.

- ☐ Verify the Truth Table and observe the outputs.

$module \ mux4\_1\_synth\_conditional(w, \, s, \, f \, );$

input [3:0] w;

input [1:0] s;

output reg f;

always @ (\*)

f = s[1]?(s[0]?w[3]:w[2]):(s[0]?w[1]:w[0]);

endmodule

RESULT: Adder and subtractor circuits are realized using multiplexer IC 74153.

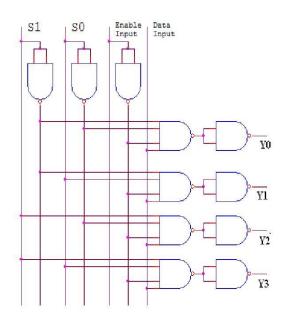

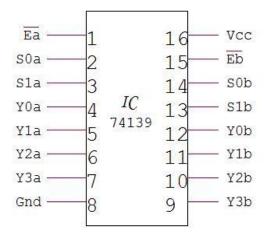

## **STUDY DEMULTIPLEXER OF IC 74LS139**:

## iii) DE-MUX USING NAND GATES

| Enable<br>Inputs | Data<br>Input | Select<br>Inputs Outputs |    |            |    |            |    |

|------------------|---------------|--------------------------|----|------------|----|------------|----|

| E                | D             | Sı                       | So | <b>Y</b> 3 | Y2 | <b>Y</b> 1 | Yo |

| 1                | 0             | X                        | X  | X          | X  | X          | X  |

| 0                | 1             | 0                        | 0  | 0          | 0  | 0          | 1  |

| 0                | 1             | 0                        | 1  | 0          | 0  | 1          | 0  |

| 0                | 1             | 1                        | 0  | 0          | 1  | 0          | 0  |

| 0                | 1             | 1                        | 1  | 1          | 0  | 0          | 0  |

## **VERIFICATION OF IC 74139 (DEMUX)**

#### TRUTH TABLE

|    | Inputs         |                | Outputs    |                |    |                |

|----|----------------|----------------|------------|----------------|----|----------------|

| Ea | S <sub>1</sub> | S <sub>0</sub> | <b>Y</b> 3 | Y <sub>2</sub> | Y1 | Y <sub>0</sub> |

| 1  | X              | X              | 1          | 1              | 1  | 1              |

| 0  | 0              | 0              | 1          | 1              | 1  | 0              |

| 0  | 0              | 1              | 1          | 1              | 0  | 1              |

| 0  | 1              | 0              | 1          | 0              | 1  | 1              |

| 0  | 1              | 1              | 0          | 1              | 1  | 1              |

```

module decoder(I, en, Y);

module demux1_4(z,a,b,en);

input [1:0] I;

input a,b,en;

input en;

output [3:0]z;

output [3:0] Y;

reg z;

reg [3:0] Y;

always@(a or b or en)

always @(en,I)

case({en,a,b})

begin

default: z = 4'b1111;

if(en==1)

3'b100 : z = 4'b1110;

Y=4'd0;

4'b110 : z = 4'b1101;

else

3'b101 : z = 4'b1011;

case(I)

4'b111 : z = 4'b014111;

2'd0: Y= 4'b0001;

2'd1: Y= 4'b0010;

endcase

2'd2: Y= 4'b0100;

endmodule

2'd3: Y= 4'b1000;

default : Y = 4'bXXXX;

endcase

end

endmodule

```

#### PROCEDURE:

- ☐ Check all the components for their working.

- ☐ Insert the appropriate IC into the IC base.

- ☐ Make connections as shown in the circuit diagram.

- ☐ Verify the Truth Table and observe the outputs.

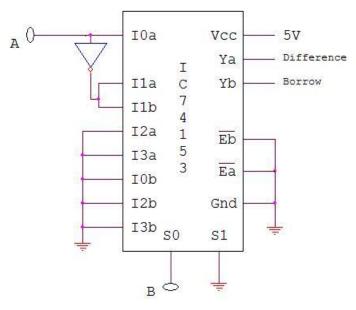

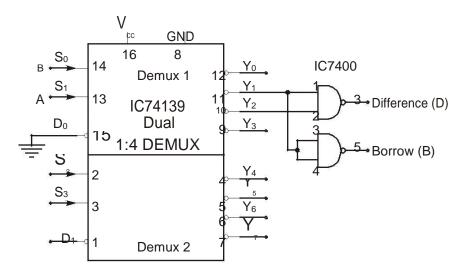

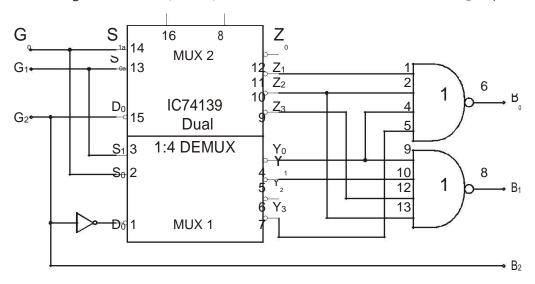

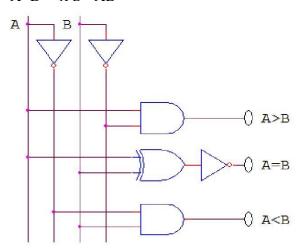

## Realization of Half Subtractor and Full Subtractor circuits using IC 74139 Chip.

## i) Half Subtractor Logic Diagram:

Figure-2: Realization of Half Subtractor using IC 74139

## Truth Table:

| Inp | outs | Out            | Outputs    |  |  |  |  |  |

|-----|------|----------------|------------|--|--|--|--|--|

| А   | В    | Difference (D) | Borrow (B) |  |  |  |  |  |

| 0   | 0    | 0              | 0          |  |  |  |  |  |

| 0   | 1    | 1              | 1          |  |  |  |  |  |

| 1   | 0    | 1              | 0          |  |  |  |  |  |

| 1   | 1    | 0              | 0          |  |  |  |  |  |

Difference  $(D) = \sum_{m} (1,2)$ Borrow  $(B_{out}) = \sum_{m} (1)$ Diffference  $(D) = \bar{A} B + A \bar{B} = A \oplus B$ Borrow  $(B_{out}) = \bar{A}B$

#### **Procedure:**

- 1) Connect the circuit as shown in figure-2 using the pin details of the IC used.

- 2) Switch on the power supply and verify the truth table of half subtractor. circuit for various input combinat

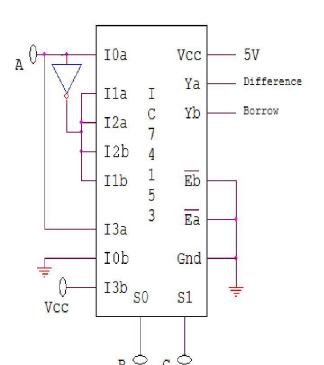

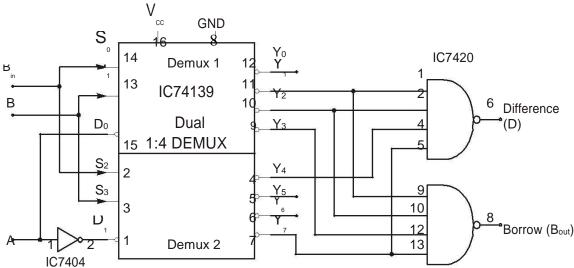

## **Logic Diagram**

Figure-3: Realization of Full Subtractor using IC 74139

#### **Truth Table:**

|   |   | Inpi | uts | Outputs    |        |                                                                                                             |

|---|---|------|-----|------------|--------|-------------------------------------------------------------------------------------------------------------|

| Г |   |      | В   | Difference | Borrow |                                                                                                             |

|   | Α | В    | In  | (D)        | (Bout) | Diffference (D) N (1.2.4.7)                                                                                 |

|   | 0 | 0    | 0   | 0          | 0      | Diffference $(D) = \sum_{m} (1,2,4,7)$<br>Borrow $(B_{out}) = \sum_{m} (1,2,3,7)$                           |

|   | 0 | 0    | 1   | 1          | 1      | Diffference $(D) = \bar{A}\bar{B}B_{in} + \bar{A}B\overline{B_{in}} + A\bar{B}\overline{B_{kn}} + ABB_{in}$ |

|   | 0 | 1    | 0   | 1          | 1      | Decree (D. ). In . In                                                                                       |

|   | 0 | 1    | 1   | 0          | 1      | Borrow $(B_{out}) = \bar{A}B + \bar{A}B_{in} + BB_{in}$                                                     |

|   | 1 | 0    | 0   | 1          | 0      |                                                                                                             |

|   | 1 | 0    | 1   | 0          | 0      |                                                                                                             |

|   | 1 | 1    | 0   | 0          | 0      |                                                                                                             |

|   | 1 | 1    | 1   | 1          | 1      |                                                                                                             |

#### **Procedure:**

- 1) Connect the circuit as shown in figure-3 using the pin details of the IC used.

- 2) Switch on the power supply and verify the truth table of full subtractor circuit for various input combinations.

#### **Result / Conclusion:**

Truth-table of 1 : 4 Demux IC, Half subtractor and Full subtractor circuits are verified.

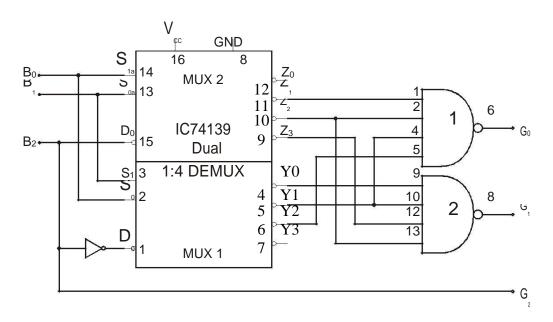

Code Converters using 74139 IC (1:4 DEMUX)

## Realization of 3-bit Binary to Gray code converter using IC 74139

Dept. of Electronics & Telecommunication Engineering, RIT. 2023-2024

## **Truth Table of Binary to Gray**

| Input          | Binary C       | odes           | Output Gray Codes |       |       |  |  |

|----------------|----------------|----------------|-------------------|-------|-------|--|--|

| B <sub>2</sub> | B <sub>1</sub> | B <sub>0</sub> | $G_2$             | $G_1$ | $G_0$ |  |  |

| 0              | 0              | 0              | 0                 | 0     | 0     |  |  |

| 0              | 0              | 1              | 0                 | 0     | 1     |  |  |

| 0              | 1              | 0              | 0                 | 1     | 1     |  |  |

| 0              | 1              | 1              | 0                 | 1     | 0     |  |  |

| 1              | 0              | 0              | 1                 | 1     | 0     |  |  |

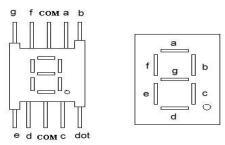

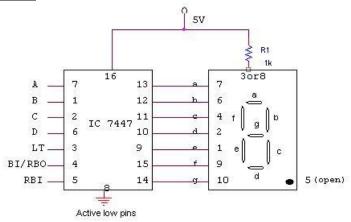

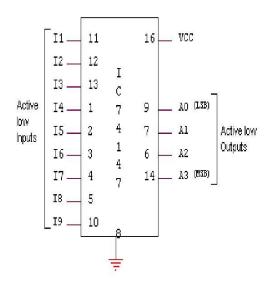

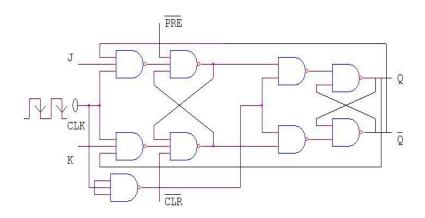

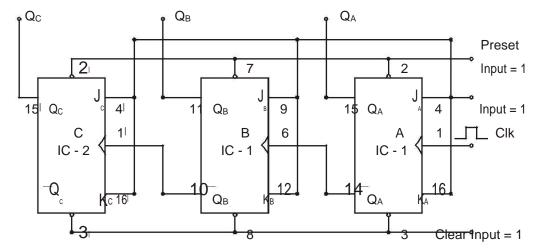

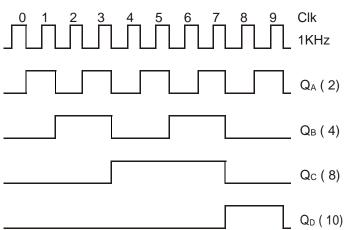

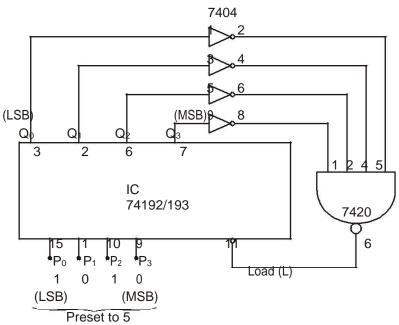

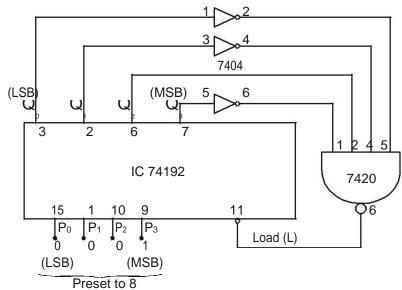

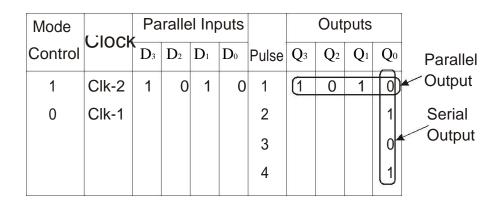

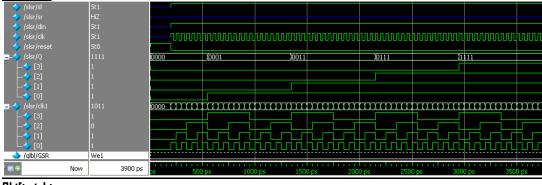

| 1              | 0              | 1              | 1                 | 1     | 1     |  |  |